# Verdin Computer Module Carrier Board Design Guide

# Verdin Carrier Board Design Guide

| Issued by:               | Toradex | Document Type: Carrier Board Design Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Purpose:                 |         | a guideline for developing a carrier board that conforms to the he Verdin Computer Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Document<br>Version:     | V1.2    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Revision History<br>Date | Version | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| June 30, 2020            | V0.9    | Initial Release: Preliminary Version                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

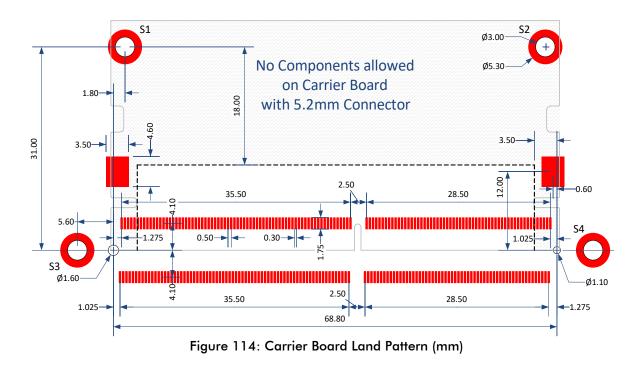

| October 16, 2020         | V0.91   | Correct position of standoff holes in carrier board land pattern drawing (Figure 114)<br>Remove additional notches from the drawings of the module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| October 28, 2020         | V0.92   | Correction of CTRL_SLEEP_MOCI# signal type from open drain to CMOS<br>Correction of standoff hole position in Figure 3<br>Section 2.6: add information to DSI display adapters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| January 5, 2021          | V0.93   | Replace front picture<br>Section 2.5.2.2: Change HDMI ESD protection IC in reference schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| February 5, 2021         | V0.94   | Add section 3.5 Backfeeding<br>Section 2.2.2.3: Update figure 10<br>Section 2.3.2.2: Update figure 15<br>Section 2.5.2.1: Update figure 28<br>Section 2.7.2: Update figure 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| May 17, 2021             | V1.0    | Section 2.10: Add warning for using a different debug UART<br>Section 2.20: Clarify module recovery<br>Section 3: Clarify sustained and peak power consumption<br>Section 3.1: Update title<br>Section 4.4 and 4.5: Clarify requirements for spacers and standoffs<br>Minor changes<br>Remove preliminary indication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| June 14, 2021            | V1.1    | Updated the PHY status LED signal names according to the 1.3 version of the<br>Verdin Family Specification throughout the whole document                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Sep 15, 2022             | V1.2    | Section 2.3.1.2.1: Update reference schematics<br>Section 2.3.1.2.2: Update reference schematics<br>Section 2.3.1.2.3: Update reference schematics<br>Section 2.3.1.3: Add capacitive coupling section, including new reference<br>schematics<br>Section 2.3.2: Clarify I/O voltage of RGMII interface<br>Section 2.4: Add USB-C information to the USB section, including new reference<br>schematics<br>Section 2.4: Add USB-C information to the USB section, including new reference<br>schematics<br>Section 2.4.3.1: Update reference schematics<br>Section 2.4.3.1: Update reference schematics<br>Section 2.4.3.1.2: Update reference schematics<br>Section 2.4.3.1.3: Update reference schematics<br>Section 2.4.3.2.3: Update reference schematics<br>Section 2.4.3.2.4: Update reference schematics<br>Section 2.4.3.2.4: Update reference schematics<br>Section 2.6.2.1: Update reference schematics<br>Section 2.6.2.1: Update reference schematics<br>Section 2.6.2.2: Update reference schematics<br>Section 2.6.2.3: Update reference schematics<br>Section 2.6.2.3: Update reference schematics<br>Section 2.6.2.4: Update reference schematics<br>Section 2.6.2.4: Update reference schematics<br>Section 2.6.2.5: Update reference schematics<br>Section 2.6.2.6: Update reference schematics<br>Section 2.7.3: Update reference schematics<br>Section 2.1.5.2: Update reference schematics<br>Section 2.1.5.2: Update reference schematics<br>Section 2.1.5.2: Update reference schematics<br>Section 2.2.0: Change port type to USB-C in reference schematics<br>Section 3.2: Correction of pull-up description of CTRL_WAKE1_MICO# signal<br>Minor changes |

# Contents

| 1   | Introductio                                                               | on                                                                           | 7    |

|-----|---------------------------------------------------------------------------|------------------------------------------------------------------------------|------|

| 1.1 | Overview                                                                  |                                                                              | 7    |

| 1.2 | Additional I                                                              | Documents                                                                    | 7    |

|     |                                                                           | out Design Guide                                                             |      |

|     |                                                                           | din Module Datasheets                                                        |      |

|     |                                                                           | din Module Definition                                                        |      |

|     |                                                                           | adex Developer Center                                                        |      |

|     |                                                                           | din Reference Designs                                                        |      |

|     |                                                                           | but Designer                                                                 |      |

| 1.3 | Abbreviatio                                                               | ns                                                                           | 8    |

| 2   | Interfaces                                                                |                                                                              | 11   |

| 2.1 |                                                                           | e                                                                            |      |

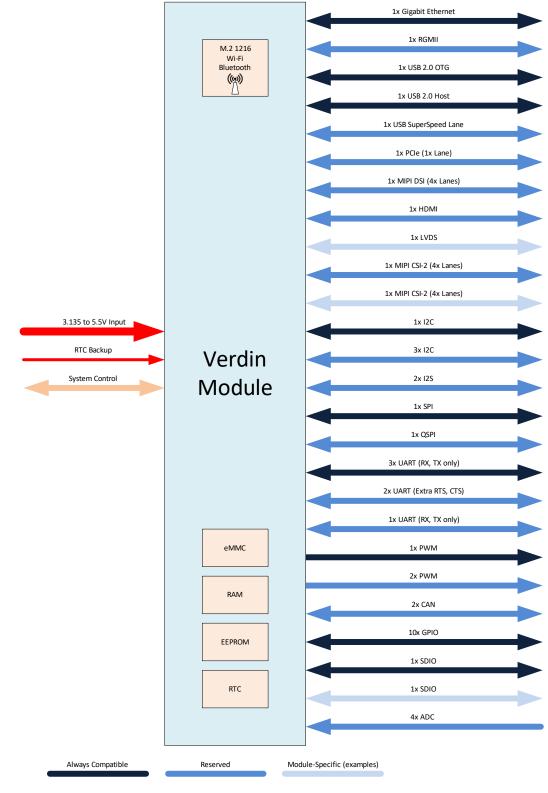

|     | 2.1.1 "Alw                                                                | /ays Compatible" Interfaces                                                  | 12   |

|     |                                                                           | served" Interfaces                                                           |      |

|     |                                                                           | dule-specific" Interfaces                                                    |      |

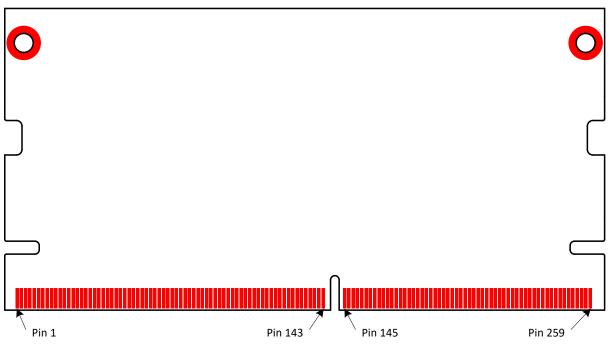

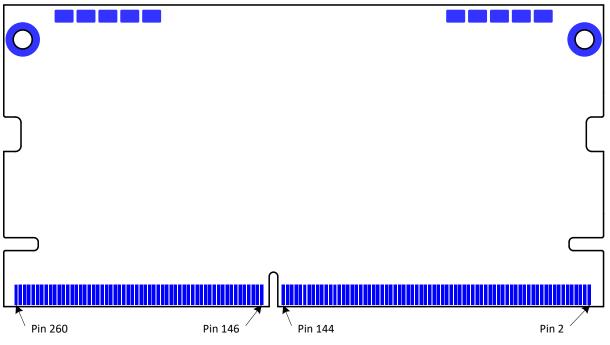

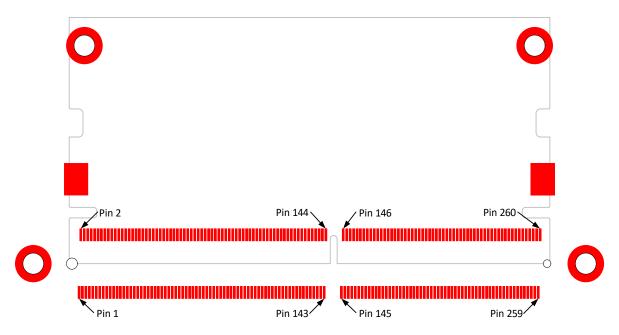

|     | 2.1.4 Pin                                                                 | Numbering                                                                    | 14   |

| 2.2 | •                                                                         | S                                                                            |      |

|     |                                                                           | e Signals                                                                    |      |

|     |                                                                           | erence Schematics                                                            |      |

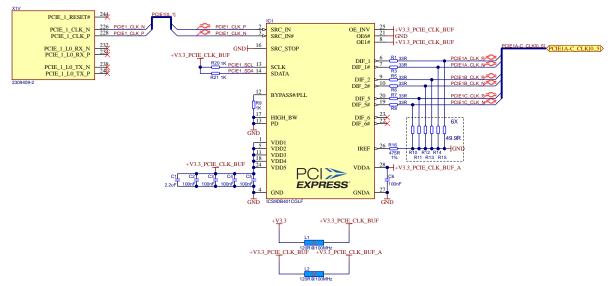

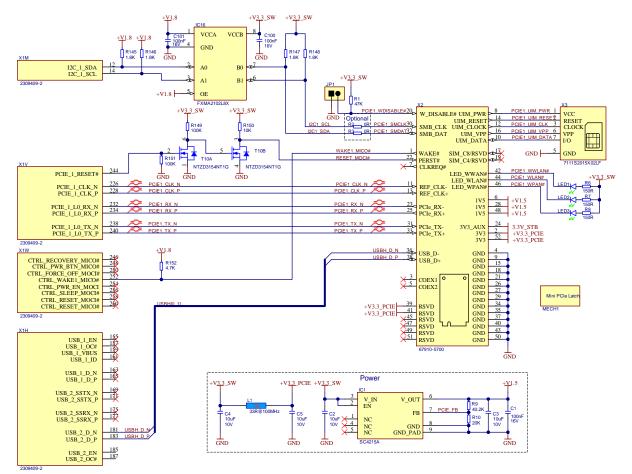

|     | 2.2.2.1                                                                   | PCIe x1 Slot Connector Schematic Example                                     |      |

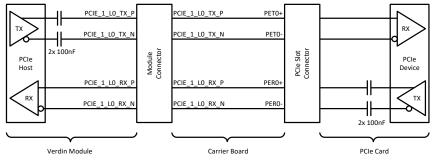

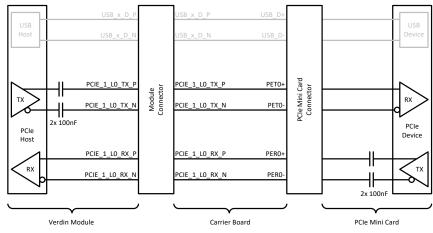

|     | 2.2.2.2                                                                   | Mini PCIe Card Schematic Example                                             |      |

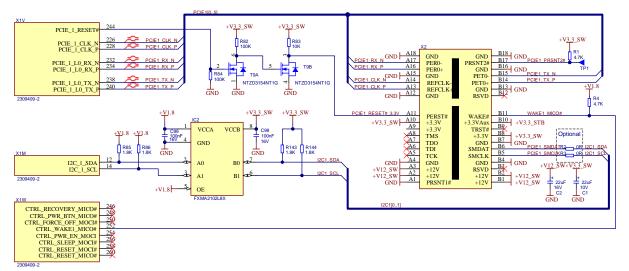

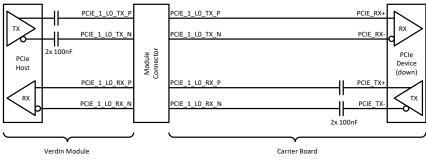

|     | 2.2.2.3                                                                   | PCIe x1 Device-Down Schematic Example                                        |      |

|     |                                                                           | sed PCIe Signals Termination                                                 |      |

| 2.3 |                                                                           |                                                                              |      |

|     |                                                                           | lia Dependent Ethernet Port                                                  |      |

|     | 2.3.1.1                                                                   | Media Dependent Ethernet Signals                                             |      |

|     | 2.3.1.2                                                                   | Media Dependent Ethernet Reference Schematics                                |      |

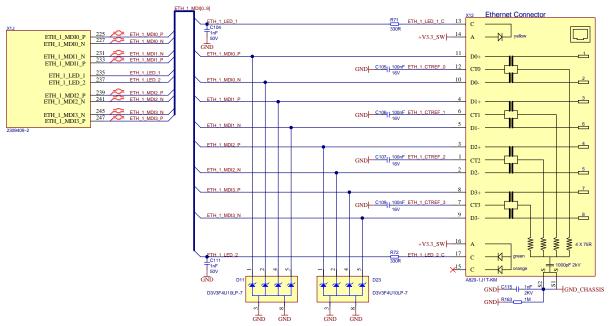

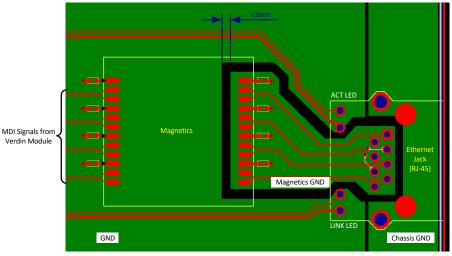

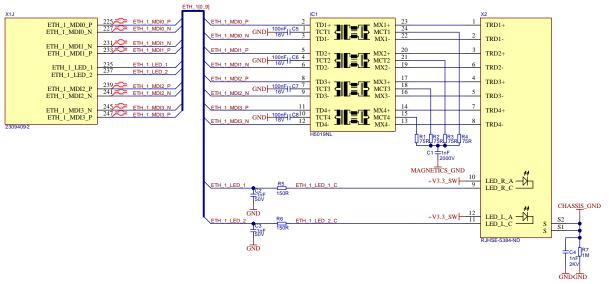

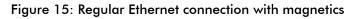

|     | 2.3.1.2.1                                                                 |                                                                              |      |

|     | 2.3.1.2.2                                                                 |                                                                              |      |

|     | 2.3.1.2.3                                                                 |                                                                              |      |

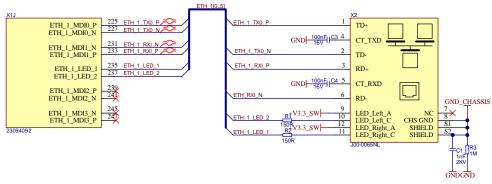

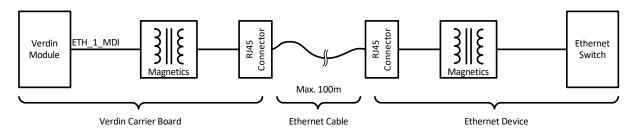

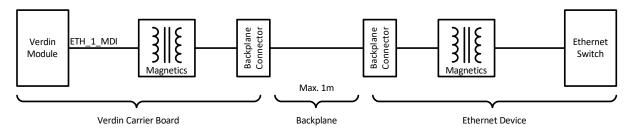

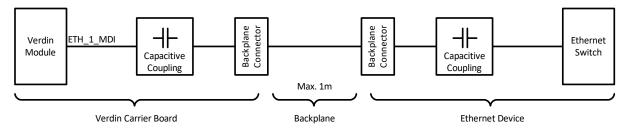

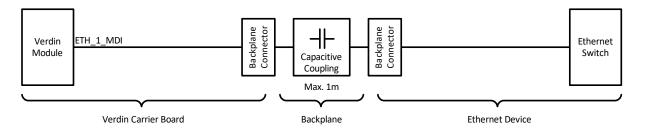

|     | 2.3.1.3                                                                   | Capacitive Coupling of Media Dependent Interfaces                            |      |

|     | 2.3.1.3.1                                                                 |                                                                              |      |

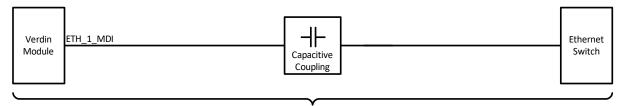

|     | 2.3.1.3.2                                                                 | Past Ethernet Capacitive Coupling with Current-Mode PHY Schematic Exam<br>27 | ipie |

|     | 2.3.1.4                                                                   | Unused Ethernet Signals Termination                                          |      |

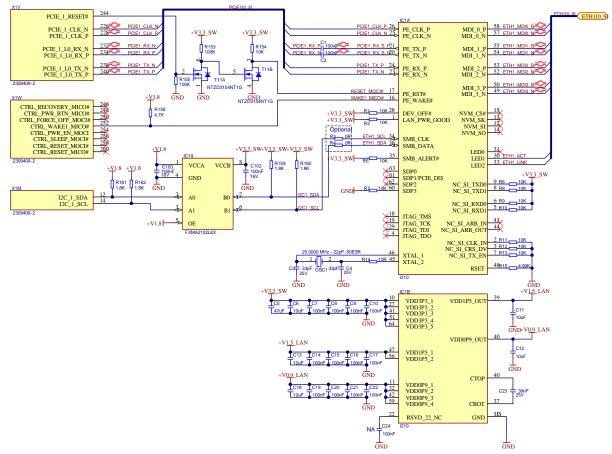

|     | 2.3.2 Red                                                                 | luced Gigabit Media-Independent Interface Ethernet Port                      |      |

|     | 2.3.2.1                                                                   | RGMII Signals                                                                |      |

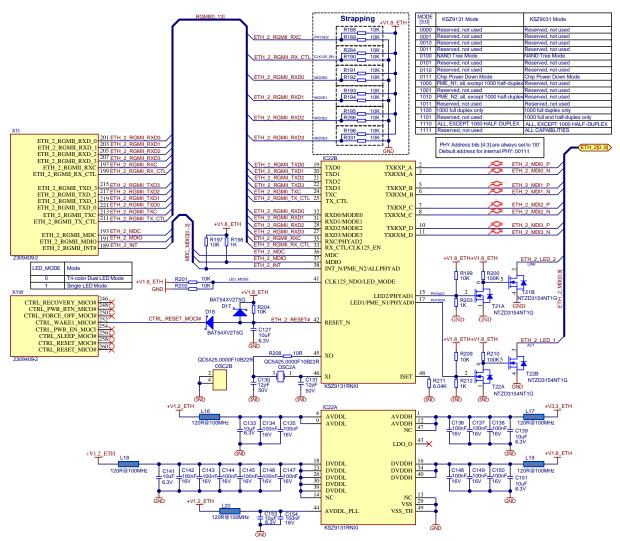

|     | 2.3.2.2                                                                   | RGMII Reference Schematics                                                   |      |

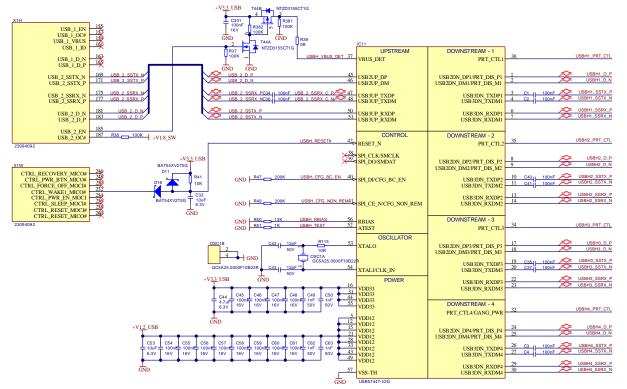

| 2.4 | USB                                                                       |                                                                              | 29   |

|     |                                                                           | 3 Signals                                                                    |      |

|     |                                                                           | 3-C                                                                          |      |

|     | 2.4.2.1                                                                   | USB-C Power Delivery                                                         | 33   |

|     | 2.4.3 Refe                                                                | erence Schematics                                                            |      |

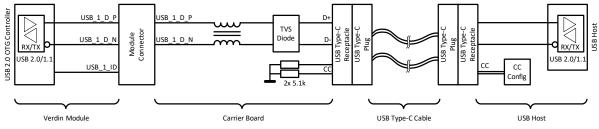

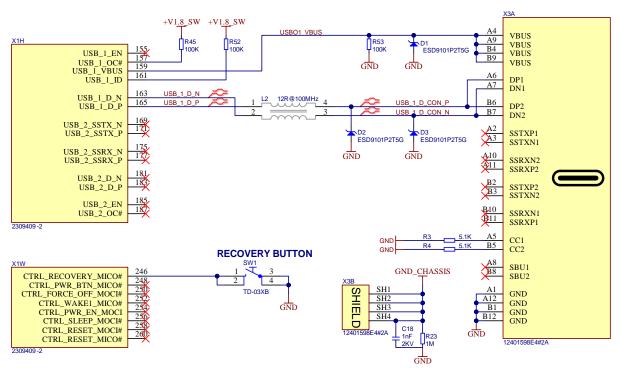

|     | 2.4.3.1                                                                   | Dual Role / Client and Host                                                  | 35   |

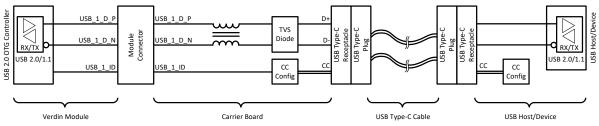

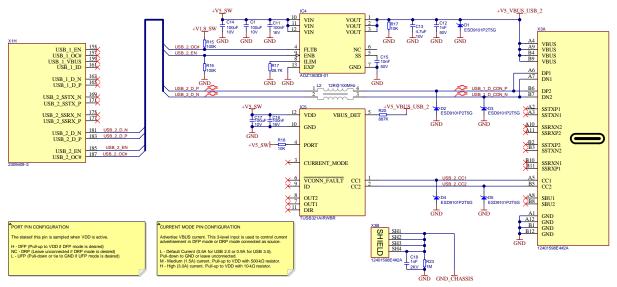

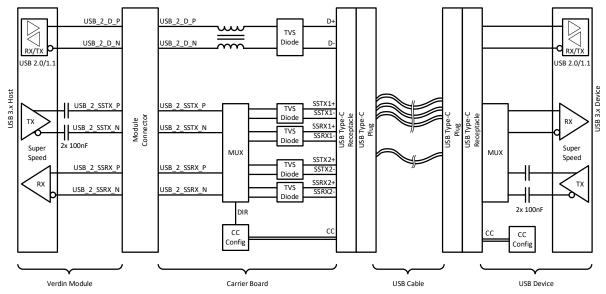

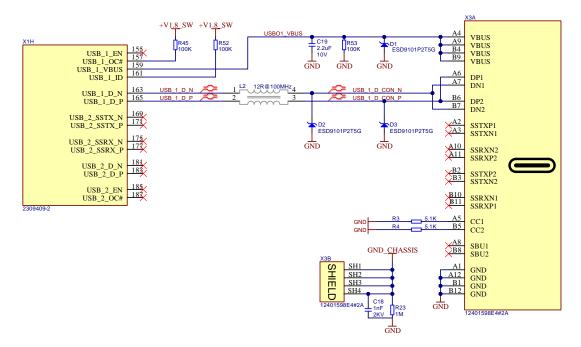

|     | 2.4.3.1.1                                                                 | USB-C High-Speed Dual Role (With Type-C Connector)                           | 35   |

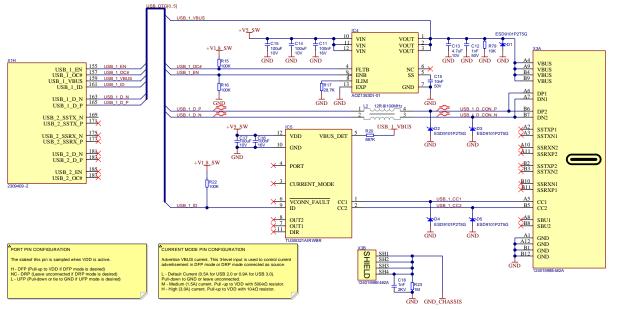

|     | 2.4.3.1.2                                                                 | USB-C SuperSpeed Dual Role (With Type-C Connector)                           | 36   |

|     | 2.4.3.1.3                                                                 |                                                                              |      |

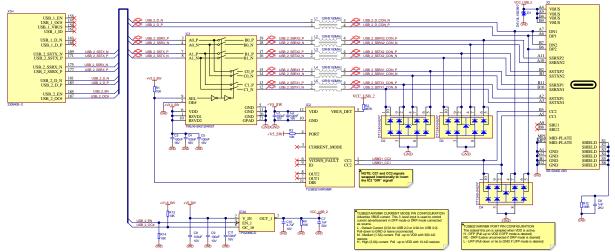

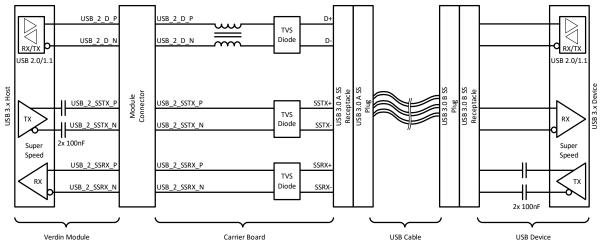

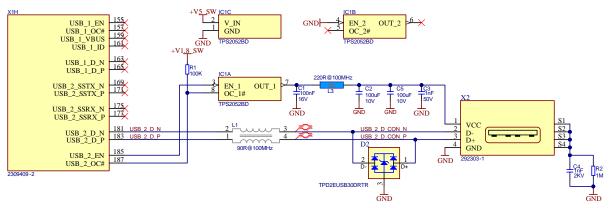

|     | 2.4.3.2                                                                   | Downstream-Facing / Host-Only                                                | 38   |

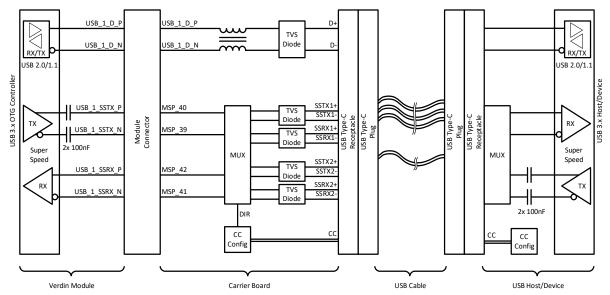

|     |                                                                           | USB-C High-Speed Downstream-Facing-Only (With Type-C Connector)              | 38   |

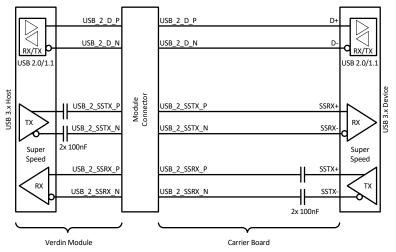

|     | 2.4.3.2.2 USB-C SuperSpeed Downstream-Facing-Only (With Type-C Connector) |                                                                              |      |

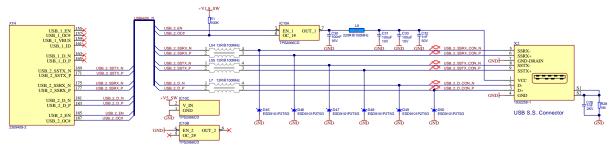

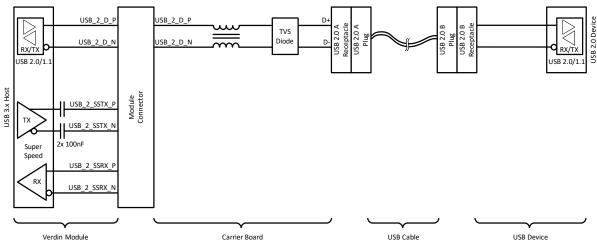

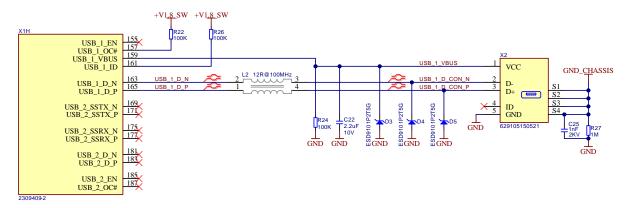

|     | 2.4.3.2.3                                                                 | USB SuperSpeed Host-Only (With Type-A Connector)                             | 40   |

|     | 2.4.3.2.4                                                                 |                                                                              |      |

|     | 2.4.3.3                                                                   | Upstream-Facing / Client-Only                                                | 42   |

| 2.4.3.3.1 USB-C High-Speed Upstream-Facing-Only (With Type-C Connector) | 42 |

|-------------------------------------------------------------------------|----|

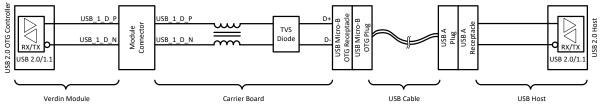

| 2.4.3.3.2 USB High-Speed Client-Only (With Type Micro-B Connector)      |    |

| 2.4.3.4 Device-Down                                                     |    |

| 2.4.3.4.1 USB High-Speed Device-Down (Without Connector)                |    |

| 2.4.4 Unused USB Signal Termination                                     |    |

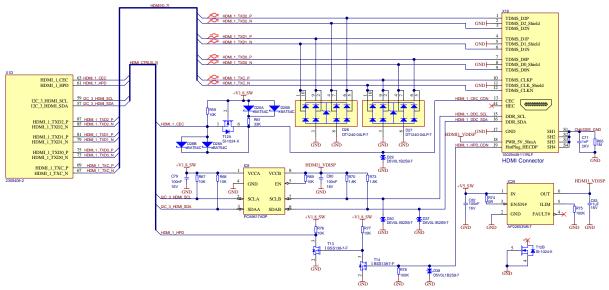

| 2.5 HDMI/DVI                                                            |    |

| 2.5 1 HDMI/DVI Signals                                                  |    |

| 2.5.1 Reference Schematics                                              |    |

| 2.5.2 Reference Schematics                                              |    |

| 2.5.2.1 DVI Schematic Example                                           |    |

| 2.5.2.2 HDM Schematic Example                                           |    |

|                                                                         |    |

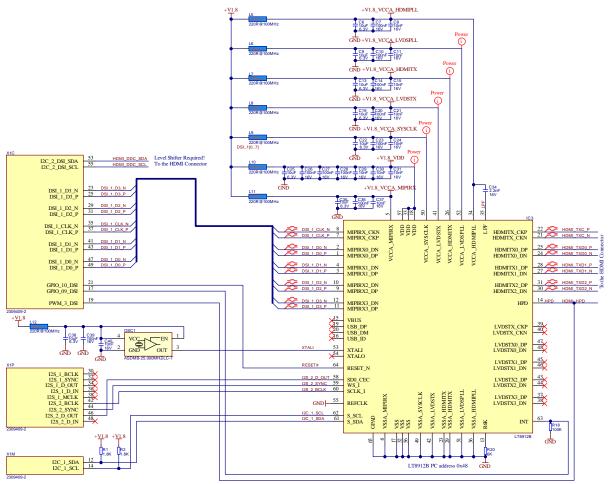

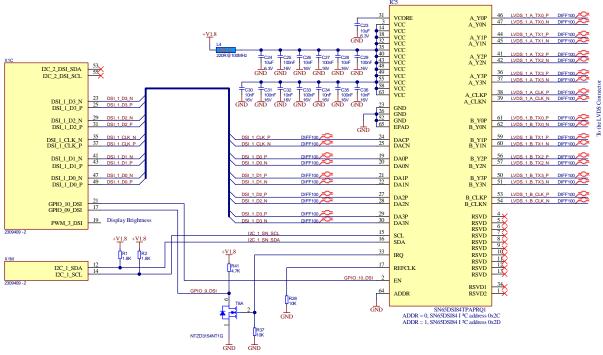

| 2.6 Display Serial Interface (MIPI DSI)                                 |    |

| 2.6.1 MIPI DSI Signals                                                  |    |

| 2.6.2 Reference Schematics                                              |    |

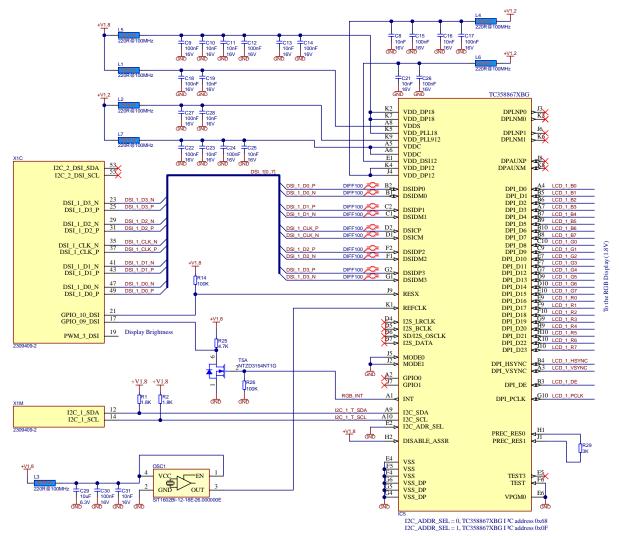

| 2.6.2.1 DSI to HDMI Schematic Example                                   |    |

| 2.6.2.2 DSI to LVDS Schematic Example                                   |    |

| 2.6.2.3 DSI to Parallel RGB Schematic Example                           |    |

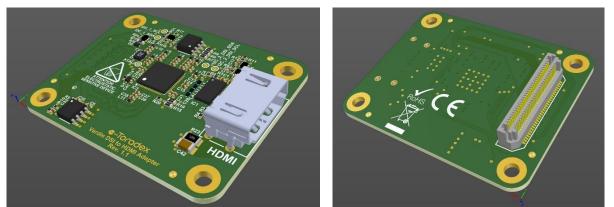

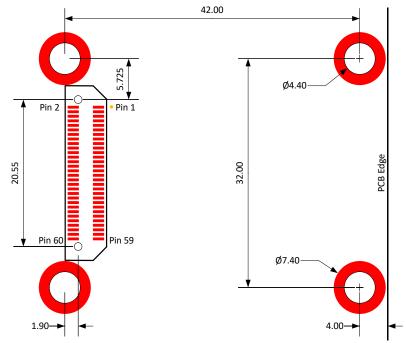

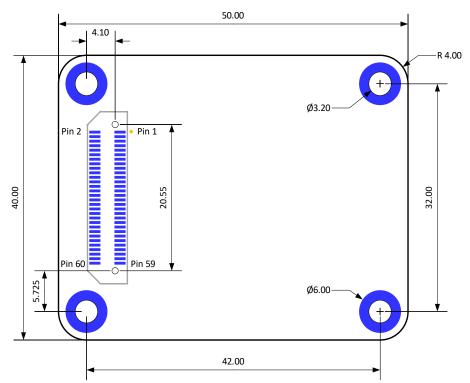

| 2.6.3 MIPI DSI Display Adapters                                         |    |

| 2.6.4 Unused MIPI DSI Signal Termination                                |    |

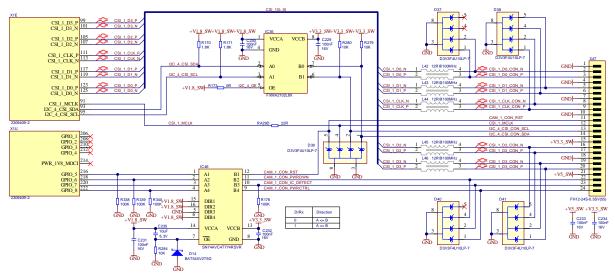

| 2.7 Camera Serial Interface (MIPI CSI-2)                                |    |

| 2.7.1 MIPI CSI-2 Signals                                                |    |

| 2.7.2 Reference Schematics                                              |    |

| 2.7.3 Unused MIPI CSI-2 Signal Termination                              | 57 |

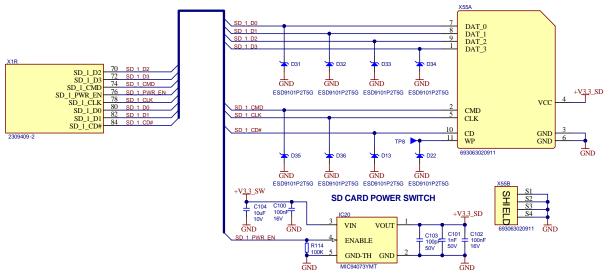

| 2.8 SD/MMC/SDIO                                                         | 57 |

| 2.8.1 SD/MMC/SDIO Signals                                               | 58 |

| 2.8.2 Reference Schematics                                              |    |

| 2.8.3 Unused SD/MMC/SDIO Interface Signal Termination                   | 59 |

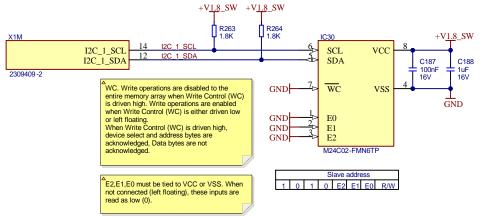

| 2.9 l <sup>2</sup> C                                                    |    |

| 2.9.1 I <sup>2</sup> C Signals                                          |    |

| 2.9.2 Reference Schematics                                              |    |

| 2.9.3 Unused I <sup>2</sup> C Signal Termination                        |    |

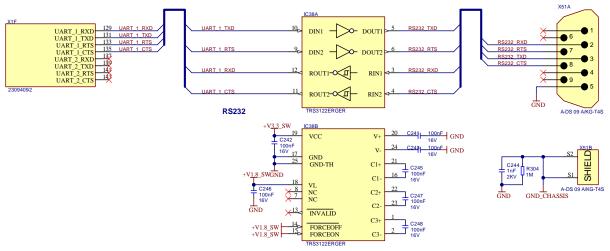

| 2.10 UART                                                               |    |

| 2.10.1 UART Signals                                                     |    |

| 2.10.2 Reference Schematics                                             |    |

| 2.10.2.1 RS232 Reference Schematics                                     |    |

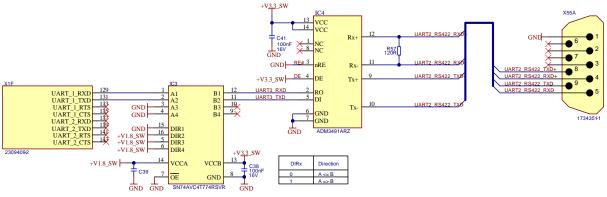

| 2.10.2.2 RS422 Reference Schematics                                     |    |

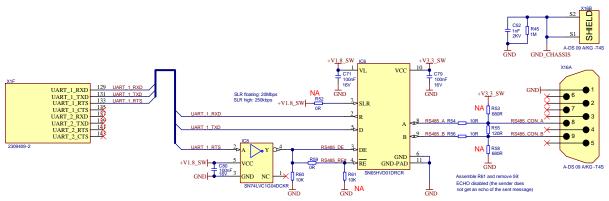

| 2.10.2.3 RS485 Reference Schematics                                     |    |

| 2.10.3 Unused UART Signal Termination                                   |    |

| 2.10.5 Ondsed OART Signal Termination                                   |    |

| 2.11.3 SPI Signals                                                      |    |

|                                                                         |    |

|                                                                         |    |

| 2.12 Quad Serial Peripheral Interface (Quad SPI)                        |    |

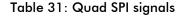

| 2.12.1 Quad SPI Signals                                                 |    |

| 2.12.2 Unused Quad SPI Signal Termination                               |    |

| 2.13 CAN                                                                |    |

| 2.13.1 CAN Signals                                                      |    |

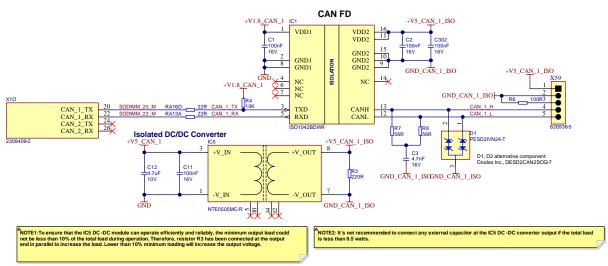

| 2.13.2 Reference Schematics                                             |    |

| 2.13.3 Unused CAN Interface Signal Termination                          |    |

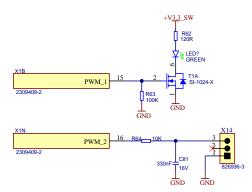

| 2.14 PWM                                                                |    |

| 2.14.1 PWM Signals                                                      |    |

| 2.14.2 Reference Schematics                                             |    |

| 2.14.3 Unused PWM Signal Termination                                    | 66 |

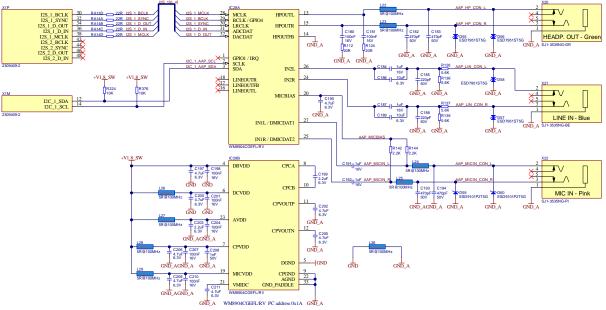

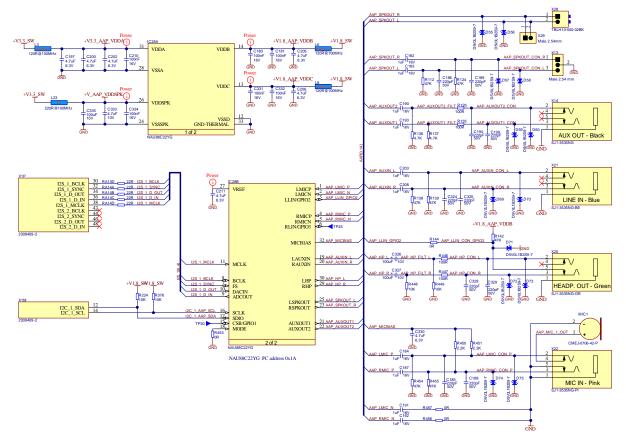

| 2.15 Inter-IC Sound (I <sup>2</sup> S)                                  | 67 |

| 2.15.1 Digital Audio Signals                                            |    |

| 2.15.2 Reference Schematics                                             |    |

| 2.15.3 Unused Digital Audio Interface Signal Termination                |    |

| 2.16 Analog Inputs                                                      |    |

|                                                                         |    |

| 2.16.1               | Analog Input Signals                                       | .69  |

|----------------------|------------------------------------------------------------|------|

| 2.16.2               | Jnused Analog Inputs Signal Termination                    | .69  |

|                      | Purpose Clock Outputs                                      |      |

|                      | Clock Output Signals                                       |      |

| 2.17.2               | Schematic and Layout Considerations                        | .69  |

| 2.17.3               | Jnused Clock Output Signal Termination                     | .70  |

| 2.18 GPIO            |                                                            | . 70 |

| 2.18.1               | GPIO Signals                                               | .70  |

| 2.18.2               | Jnused GPIO Termination                                    | .70  |

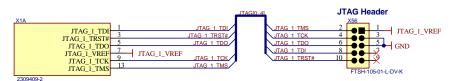

| 2.19 JTAG inte       | rface                                                      | . 70 |

| 2.19.1               | JTAG Signals                                               | .71  |

|                      | Reference Schematics                                       |      |

| 2.19.3               | Jnused JTAG Signal Termination                             | .71  |

| 2.20 Module R        | ecovery                                                    | .71  |

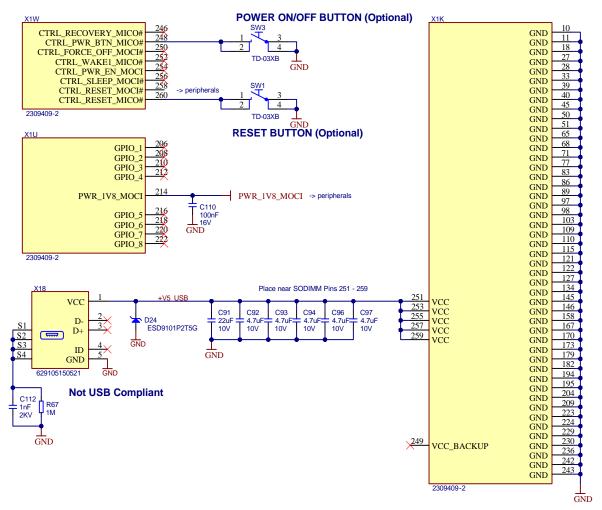

| 2.20.1 I             | Recovery Signals                                           | .72  |

| 2.20.2               | Reference Schematics                                       | .72  |

| 2.20.3               | Jnused Recovery Signal Termination                         | .72  |

|                      |                                                            | 70   |

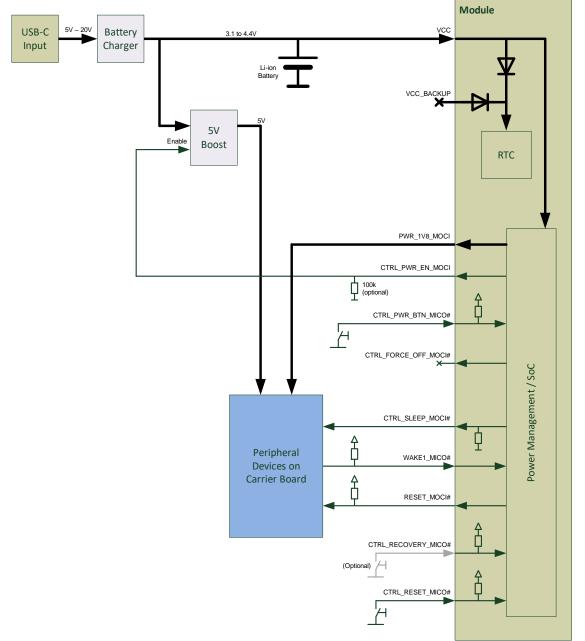

|                      | anagement                                                  |      |

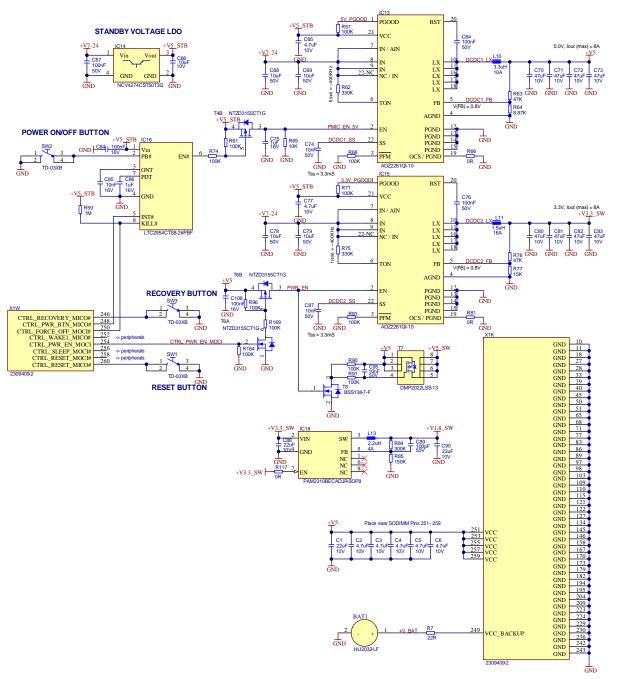

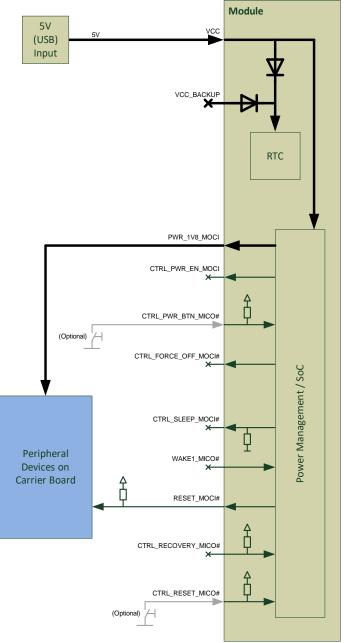

|                      | pply Design                                                |      |

|                      | wer Supply Signals                                         |      |

|                      | wer Management Signals                                     |      |

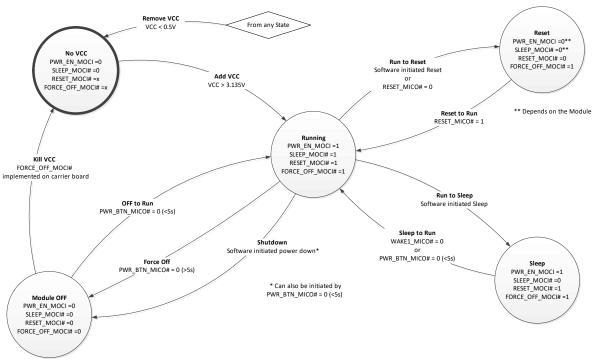

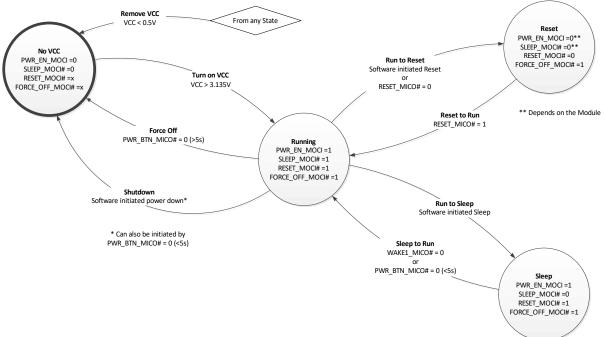

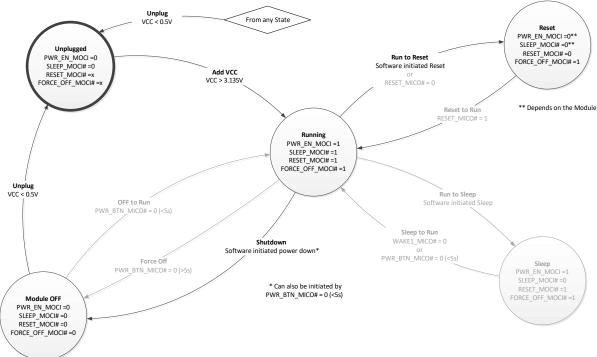

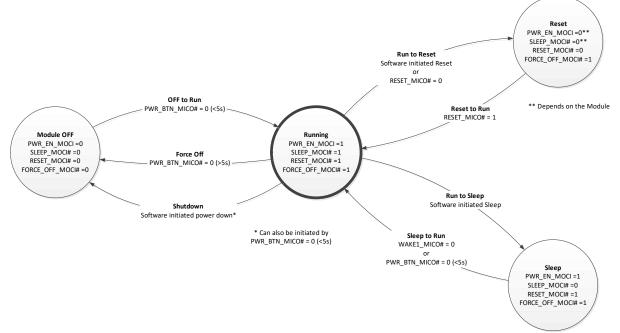

|                      | ower States                                                |      |

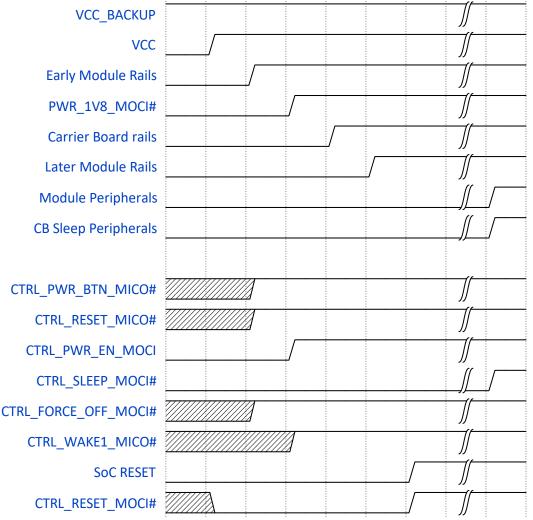

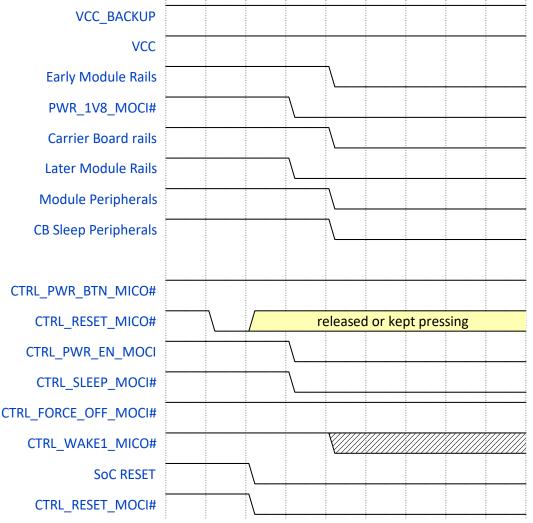

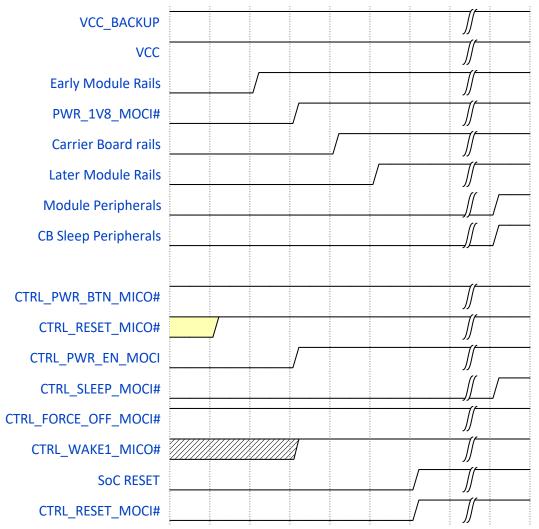

|                      | Power Sequences                                            |      |

|                      | o VCC" to "Running" (startup)                              |      |

|                      | unning" to "Reset" (reset)                                 |      |

|                      | eset" to "Running" (startup after reset)                   |      |

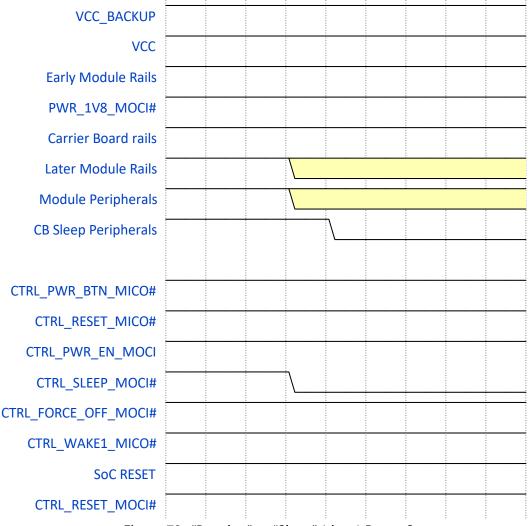

|                      | unning" to "Sleep" (sleep)                                 |      |

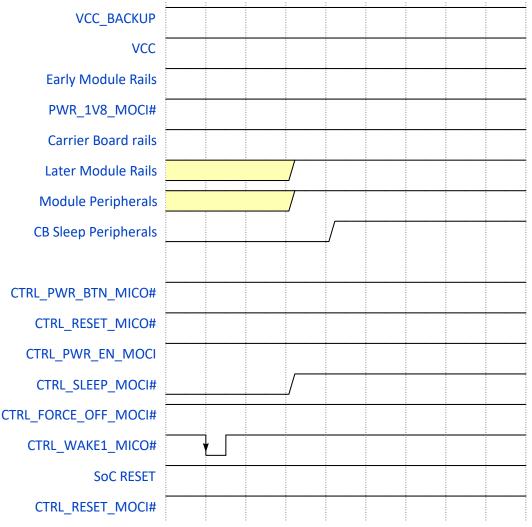

|                      | eep" to "Running" (wake)                                   |      |

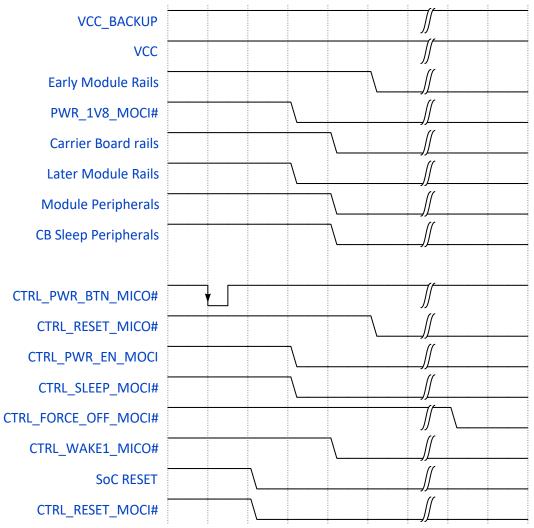

| 3.3.6 "R             | unning" to "Module OFF" (shutdown)                         | .82  |

|                      | unning" to "No VCC" (force-off)                            |      |

|                      | odule OFF" to "Running" (startup after shutdown)           |      |

|                      | odule OFF" to "No VCC" (power off after shutdown)          |      |

|                      | Remove VCC in any power state                              |      |

|                      | pply Use Cases                                             |      |

|                      | vitched VCC Approach (Verdin Development Board)            |      |

| 3.4.1.1              | Power Block Diagram                                        |      |

|                      | System Power States                                        |      |

| 3.4.1.3              | Reference Schematics                                       |      |

|                      | nimalist Carrier Board Power Approach                      |      |

| 3.4.2.1              | Power Block Diagram                                        |      |

| 3.4.2.2<br>3.4.2.3   | System Power States                                        |      |

|                      | Reference Schematics                                       |      |

|                      | ngle Cell Battery Power Approach                           |      |

| 3.4.3.1<br>3.4.3.2   | Power Block Diagram System Power States                    |      |

| 3.4.3.2              | Reference Schematics                                       |      |

|                      |                                                            |      |

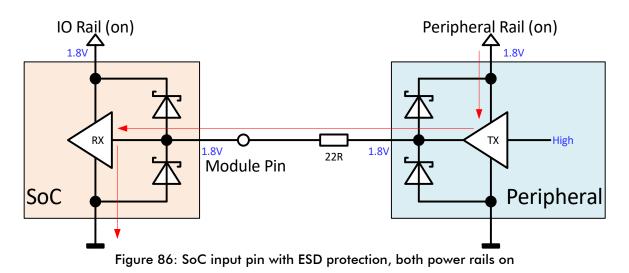

|                      | ng                                                         |      |

|                      | roduction                                                  |      |

|                      | nat is Backfeeding<br>tential Issues Caused by Backfeeding |      |

|                      | · •                                                        |      |

| 3.5.4 Ide<br>3.5.4.1 | entify Backfeeding Issues                                  |      |

| 3.5.4.1              | System Design                                              |      |

|                      | Prototype Testing                                          |      |

| з.э.э ва<br>3.5.5.1  | ckfeeding Prevention                                       |      |

| 3.5.5.1<br>3.5.5.2   | Avoid Multiple Power Domains                               |      |

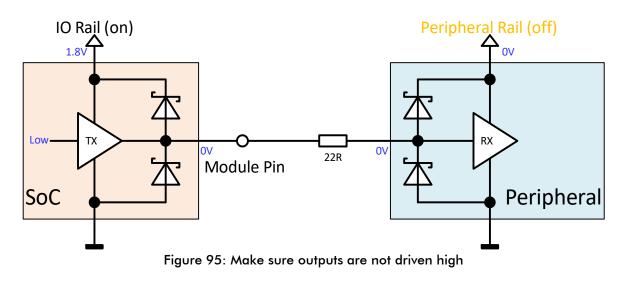

|                      | Avoid Driving Outputs High                                 |      |

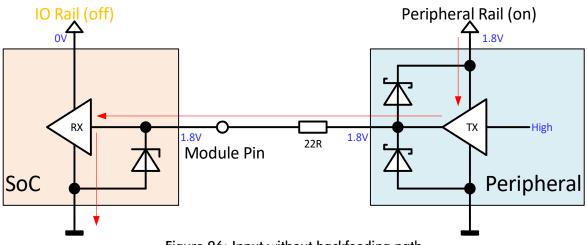

| 3.5.5.3              | Inputs without Backfeeding Path                            | 103  |

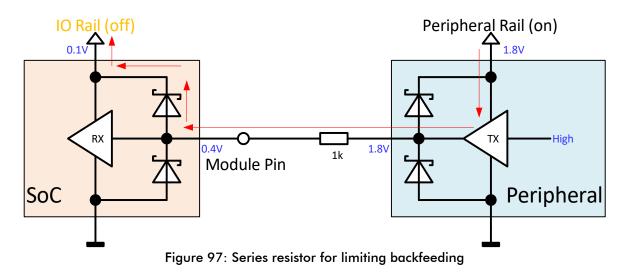

|             | 3.5.5.4                                           | Series Resistor                           | 103 |  |  |  |  |

|-------------|---------------------------------------------------|-------------------------------------------|-----|--|--|--|--|

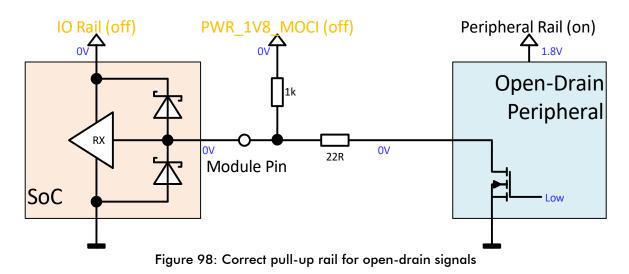

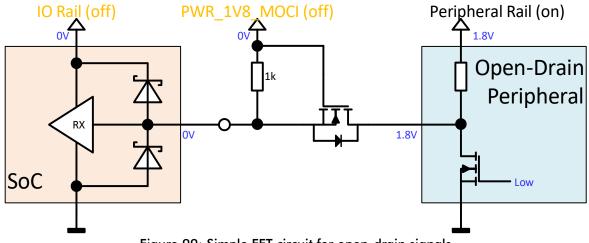

|             | 3.5.5.5                                           | Open Drain Signals                        |     |  |  |  |  |

|             | 3.5.5.6                                           | Simple FET Circuit for Open-Drain Signals | 104 |  |  |  |  |

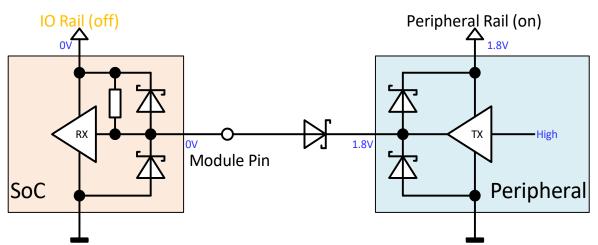

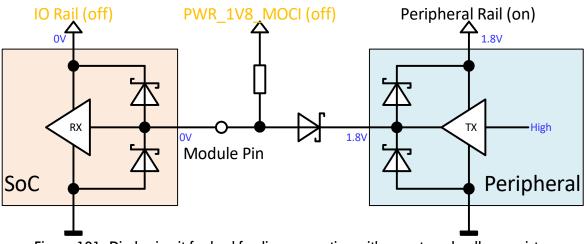

|             | 3.5.5.7                                           | Blocking Diode                            |     |  |  |  |  |

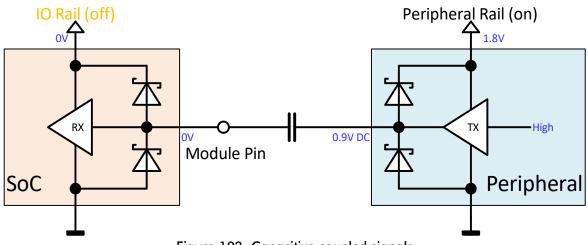

|             | 3.5.5.8                                           | Capacitive Coupling                       | 106 |  |  |  |  |

|             | 3.5.5.9                                           | Non-Backfeeding Buffer                    | 106 |  |  |  |  |

|             | 3.5.5.10                                          | Dual-FET circuit                          | 107 |  |  |  |  |

|             | 3.5.5.11                                          | Tristate Buffer                           | 107 |  |  |  |  |

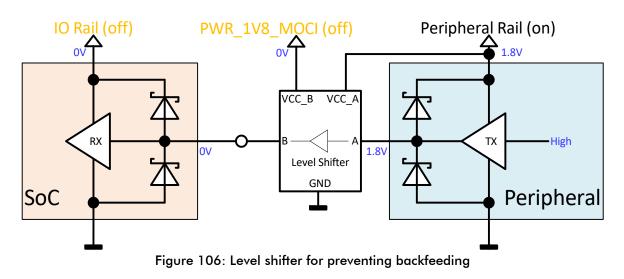

|             | 3.5.5.12                                          | Level Shifter                             | 108 |  |  |  |  |

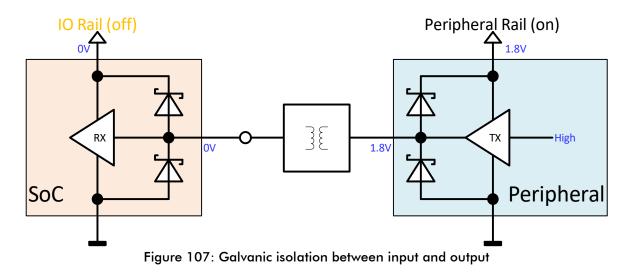

|             | 3.5.5.13                                          | Galvanic Isolation                        |     |  |  |  |  |

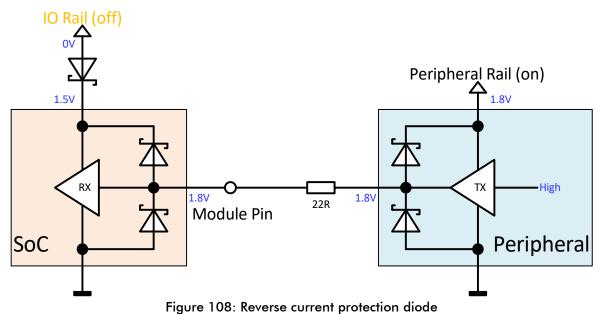

|             | 3.5.5.14                                          | Reverse Current Protection in IO Rail     | 109 |  |  |  |  |

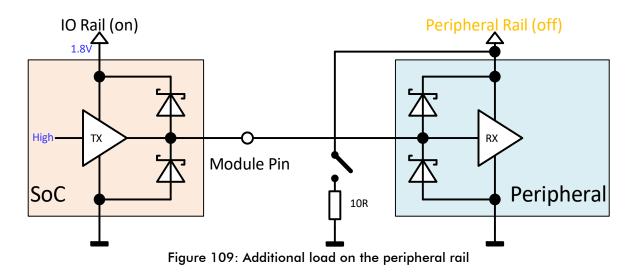

|             | 3.5.5.15                                          | Extra Load on Rail                        | 109 |  |  |  |  |

| 4           | Machanic                                          | al and Thermal Consideration              | 110 |  |  |  |  |

| <b>4</b> .1 |                                                   |                                           |     |  |  |  |  |

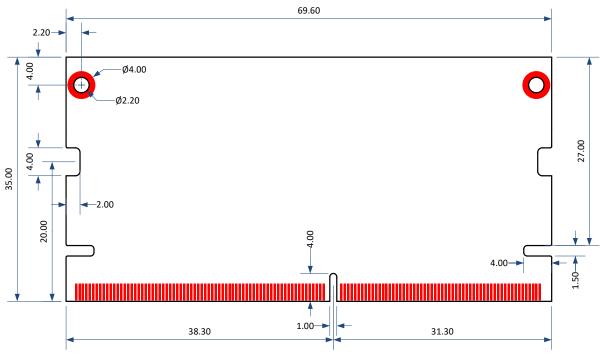

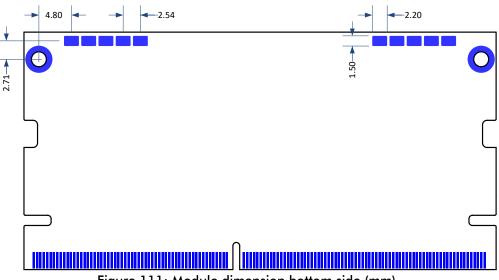

| 4.1         |                                                   | Module Dimensions                         |     |  |  |  |  |

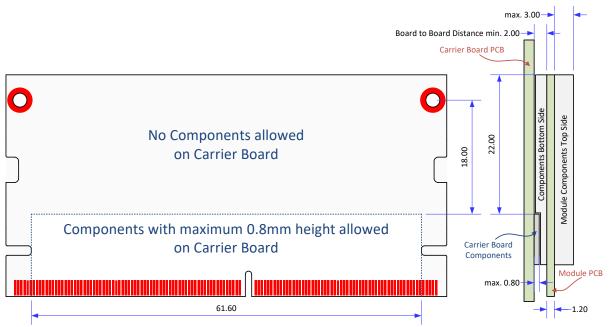

|             | Module Connector and Stacking Height              |                                           |     |  |  |  |  |

| 4.3         |                                                   | Fixation of the Module                    |     |  |  |  |  |

| 4.4         | Thermal Solution                                  |                                           |     |  |  |  |  |

|             |                                                   | rdin Industrial Heatsink                  |     |  |  |  |  |

|             |                                                   | din Clip-on Heatsink                      |     |  |  |  |  |

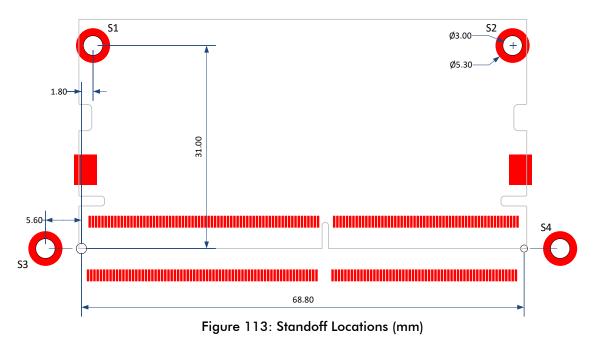

| 4.5         |                                                   | and Standoff Land Pattern Requirements    |     |  |  |  |  |

| 4.6         | Carrier Boa                                       | ard Space Requirements                    | 114 |  |  |  |  |

| 5           | Appendix A – Module Top Side Signal Definition115 |                                           |     |  |  |  |  |

| 6           | Appendix                                          | B – Module Bottom Side Signal Definition  | 119 |  |  |  |  |

| 7           | Appendix                                          | C - Physical Pin Definition and Location  | 123 |  |  |  |  |

|             |                                                   | DISCLAIMER:                               |     |  |  |  |  |

# **1** Introduction

# 1.1 Overview

This document guides users through the development of a customized carrier board for the Verdin System-on-Module (SoM) family. It describes the different interfaces of those modules and provides reference schematics as well. The document highlights standardized features of Verdin SoMs (compatible between different modules). "Module-specific" interfaces, features, and alternate functions are not detailed in this document. These interfaces are detailed in the respective datasheets of Verdin SoMs. Some Verdin modules do not feature the complete set of the "Reserved" interfaces. It is strongly recommended always to read the datasheet of the module that is intended to be used with an off-the-shelf or a custom carrier board.

Verdin modules feature new high-speed interfaces such as PCI Express, HDMI, MIPI CSI, and DSI, requiring special layout considerations regarding trace impedance and length matching. Please read the Toradex Layout Design Guide carefully for additional information on the routing of these interfaces.

# 1.2 Additional Documents

## 1.2.1 Layout Design Guide

This document contains layout requirement specifications for high-speed signals and helps to avoid issues related to layout.

https://developer.toradex.com/carrier-board-design

#### 1.2.2 Verdin Module Datasheets

For every Verdin Module, there is a datasheet available. Among other things, this document describes the "Module-specific" interfaces and secondary functionalities of pins. Before starting the development of a customized carrier board, please check these documents to verify if the required interfaces are available on the selected modules.

https://www.toradex.com/computer-on-modules/verdin-arm-family

#### 1.2.3 Verdin Module Definition

This document describes the Verdin Module standard. It provides information on the mechanical and electrical properties of Verdin modules, in addition to functionalities and interfaces provided by those modules.

The document is available soon.

#### 1.2.4 Toradex Developer Center

You can find a lot of additional information in the Toradex Developer Center, which is updated with the latest product support information regularly.

Please note that the Developer Center is common for all Toradex products. You should always check to ensure if the information is valid or relevant to the Verdin modules.

https://developer.toradex.com/

#### 1.2.5 Verdin Reference Designs

Schematic files, assembly drawings, bills of material, and the complete Altium project files for the Verdin reference carrier boards are available for download for free. There is also an online viewer available, convenient for customers without a license for Altium.

https://developer.toradex.com/carrier-board-design/reference-designs

#### 1.2.6 Pinout Designer

The Toradex Pinout Designer is a powerful tool for evaluating different pin multiplexing options for Verdin, Apalis, and Colibri Modules. Defining the pin multiplexing configuration to use or design for is a vital step in the process of designing a custom carrier board.

The tool allows comparing interfaces across different modules as well.

http://developer.toradex.com/knowledge-base/pinout-designer

| Abbreviation | Explanation                                                                                                                                   |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| ADC          | Analog to Digital Converter                                                                                                                   |  |  |  |  |

| AGND         | Analog Ground, separate ground for analog signals                                                                                             |  |  |  |  |

|              | Automatically Medium Dependent Interface Crossing, a PHY with Auto-MDIX can detect whether RX and                                             |  |  |  |  |

| Auto-MDIX    | TX need to be crossed (MDI or MDIX)                                                                                                           |  |  |  |  |

| BSP          | Board Support Package                                                                                                                         |  |  |  |  |

| CAD          | Computer-Aided Design, in this document is referred to PCB Layout tools                                                                       |  |  |  |  |

| CAN          | Controller Area Network, a bus that is mainly used in the automotive and industrial environment                                               |  |  |  |  |

| CAN FD       | Controller Area Network Flexible Data-Rate, an extension to the original CAN bus protocol, allows higher data rates and larger message sizes. |  |  |  |  |

| CEC          | Consumer Electronic Control, HDMI feature that allows controlling CEC compatible devices                                                      |  |  |  |  |

| CPU          | Central Processor Unit                                                                                                                        |  |  |  |  |

| CSI          | Camera Serial Interface                                                                                                                       |  |  |  |  |

| DAC          | Digital to Analog Converter                                                                                                                   |  |  |  |  |

| DDC          | Display Data Channel, interface for reading out the capability of a monitor, in this document DDC2B (based on $I^2C$ ) is always meant        |  |  |  |  |

| DFP          | Downstream Facing Port, USB Type-C port that acts as a host                                                                                   |  |  |  |  |

| DRC          | Design Rule Check, a tool for checking whether all design rules are satisfied in a CAD tool                                                   |  |  |  |  |

| DRD          | Dual-Role Data, USB Type-C port that can act as host or device                                                                                |  |  |  |  |

| DRP          | Dual-Role Port, USB Type-C port that can operate as power sink and source                                                                     |  |  |  |  |

| DSI          | Display Serial Interface                                                                                                                      |  |  |  |  |

| DVI          | Digital Visual Interface, digital signals are electrically compatible with HDMI                                                               |  |  |  |  |

| DVI-A        | Digital Visual Interface Analog only, signals are compatible with VGA                                                                         |  |  |  |  |

| DVI-D        | Digital Visual Interface Digital only, signals are electrically compatible with HDMI                                                          |  |  |  |  |

| DVI-I        | Digital Visual Interface Integrated, combines digital and analog video signals in one connector                                               |  |  |  |  |

| EDA          | Electronic Design Automation, software for schematic capture and PCB layout (CAD or ECAD)                                                     |  |  |  |  |

| EDID         | Extended Display Identification Data, timing setting information provided by the display in a PROM                                            |  |  |  |  |

| EMI          | Electromagnetic Interference, high-frequency disturbances                                                                                     |  |  |  |  |

| eMMC         | Embedded Multi Media Card, flash memory combined with MMC interface controller in a BGA package, used as internal flash memory                |  |  |  |  |

| ESD          | Electrostatic Discharge, high voltage spike or spark that can damage electrostatic- sensitive devices                                         |  |  |  |  |

| FPD-Link     | Flat Panel Display Link, high-speed serial interface for liquid crystal displays. In this document, it is also called the LVDS interface.     |  |  |  |  |

| GBE          | Gigabit Ethernet, Ethernet interface with a maximum data rate of 1000Mbit/s                                                                   |  |  |  |  |

| GMII         | Gigabit Media-Independent Interface, an interface between Ethernet MAC and PHY for up to 1Gb/s                                                |  |  |  |  |

#### 1.3 Abbreviations

| Abbreviation     | Explanation                                                                                                                                                                                                                                                                                                                                                                        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND              | Ground                                                                                                                                                                                                                                                                                                                                                                             |

| GPI              | General Purpose Input                                                                                                                                                                                                                                                                                                                                                              |

| GPIO             | General Purpose Input/Output, pin that can be configured as an input or output                                                                                                                                                                                                                                                                                                     |

| GPO              | General Purpose Output                                                                                                                                                                                                                                                                                                                                                             |

| GSM              | Global System for Mobile Communications                                                                                                                                                                                                                                                                                                                                            |

| HDA              | High Definition Audio (HD Audio), a digital audio interface between CPU and audio codec                                                                                                                                                                                                                                                                                            |

| HDCP             | High-Bandwidth Digital Content Protection, copy protection system that is used by HDMI beside others                                                                                                                                                                                                                                                                               |

| HDMI             | High-Definition Multimedia Interface, combines audio and video signal for connecting monitors, TV sets or Projectors, electrical compatible with DVI-D                                                                                                                                                                                                                             |

| I <sup>2</sup> C | Inter-Integrated Circuit, a two-wire interface for connecting low-speed peripherals                                                                                                                                                                                                                                                                                                |

| l <sup>2</sup> S | Integrated Interchip Sound, serial bus for connecting PCM audio data between two devices                                                                                                                                                                                                                                                                                           |

| IrDA             | Infrared Data Association, an infrared interface for connecting peripherals                                                                                                                                                                                                                                                                                                        |

| JTAG             | Joint Test Action Group, widely used debug interface                                                                                                                                                                                                                                                                                                                               |

| LCD              | Liquid Crystal Display                                                                                                                                                                                                                                                                                                                                                             |

| LSB              | Least Significant Bit                                                                                                                                                                                                                                                                                                                                                              |

| LVDS             | Low-Voltage Differential Signaling, an electrical interface standard that can transport high-speed signals over twisted-pair cables. Many interfaces like PCIe or SATA use this interface. Since the first successful application was the Flat Panel Display Link, LVDS became synonymous with this interface. In this document, the term LVDS is used for the FPD-Link interface. |

| MAC              | Medium Access Control is part of the second layer (data link layer) in the Ethernet stack                                                                                                                                                                                                                                                                                          |

| MII              | Media-Independent Interface, an interface between Ethernet MAC and PHY for up to 100Mb/s                                                                                                                                                                                                                                                                                           |

| MIPI             | Mobile Industry Processor Interface Alliance                                                                                                                                                                                                                                                                                                                                       |

| MDI              | Medium Dependent Interface, the physical interface between Ethernet PHY and cable connector                                                                                                                                                                                                                                                                                        |

| MDIO             | Management Data Input/Output, an interface that is used for controlling the Ethernet PHY. The bus<br>consists of the MDC clock and the MDIO bidirectional data signal.                                                                                                                                                                                                             |

| MDIX             | Medium Dependent Interface Crossed, an MDI interface with crossed RX and TX interfaces                                                                                                                                                                                                                                                                                             |

| mini PCle        | PCI Express Mini Card, a card form factor for internal peripherals. The interface features PCIe and USB 2.0 connectivity                                                                                                                                                                                                                                                           |

| MMC              | MultiMediaCard, flash memory card                                                                                                                                                                                                                                                                                                                                                  |

| MSB              | Most Significant Bit                                                                                                                                                                                                                                                                                                                                                               |

| mSATA            | Mini-SATA, a standardized form factor for small solid-state drive, similar dimensions as mini PCIe                                                                                                                                                                                                                                                                                 |

| МХМЗ             | Mobile PCI Express Module (second generation), graphic card standard for a mobile device, the Apalis<br>form factor uses the physical connector but not the pin-out and the PCB dimensions of the MXM3<br>standard.                                                                                                                                                                |

| N/A              | Not Available                                                                                                                                                                                                                                                                                                                                                                      |

| N/C              | Not Connected                                                                                                                                                                                                                                                                                                                                                                      |

| OD               | Open-Drain                                                                                                                                                                                                                                                                                                                                                                         |

| OTG              | USB On-The-Go, a USB host interface that can also act as a USB client when connected to another host interface                                                                                                                                                                                                                                                                     |

| OWR              | One Wire (1-Wire), a low-speed interface that needs just one data wire plus ground                                                                                                                                                                                                                                                                                                 |

| PCB              | Printed Circuit Board                                                                                                                                                                                                                                                                                                                                                              |

| PCI              | Peripheral Component Interconnect, parallel computer expansion bus for connecting peripherals                                                                                                                                                                                                                                                                                      |

| PCle             | PCI Express, a high-speed serial computer expansion bus, replaces the PCI bus                                                                                                                                                                                                                                                                                                      |

| PCM              | Pulse-Code Modulation, digitally representation of analog signals, standard interface for digital audio                                                                                                                                                                                                                                                                            |

| PD               | Pull-Down Resistor                                                                                                                                                                                                                                                                                                                                                                 |

| PHY              | Physical Layer of the OSI model                                                                                                                                                                                                                                                                                                                                                    |

| PMIC             | Power Management IC, an integrated circuit that manages amongst others the power sequence of a system                                                                                                                                                                                                                                                                              |

| PU               | Pull-up Resistor                                                                                                                                                                                                                                                                                                                                                                   |

| PWM              | Pulse-Width Modulation                                                                                                                                                                                                                                                                                                                                                             |

| QSPI             | Quad SPI, SPI interface with four bidirectional data signals                                                                                                                                                                                                                                                                                                                       |

| RGB              | Red Green Blue, color channels in common display interfaces                                                                                                                                                                                                                                                                                                                        |

| RGMII            | Reduced Gigabit Media-Independent Interface, an interface between Ethernet MAC and PHY for up to 1Gb/s                                                                                                                                                                                                                                                                             |

| RJ45             | Registered Jack, common name for the 8P8C modular connector that is used for Ethernet wiring                                                                                                                                                                                                                                                                                       |

| Abbreviation | Explanation                                                                                                                                                        |  |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| RMII         | Reduced Media-Independent Interface, an interface between Ethernet MAC and PHY for up to 100Mb/s                                                                   |  |  |  |  |

| RS232        | Single-ended serial port interface                                                                                                                                 |  |  |  |  |

| RS422        | Differential signaling serial port interface, full-duplex                                                                                                          |  |  |  |  |

| RS485        | Differential signaling serial port interface, half-duplex, multi-drop configuration possible                                                                       |  |  |  |  |

| R-UIM        | Removable User Identity Module, identifications card for CDMA phones and networks, an extension of the GSM SIM card                                                |  |  |  |  |

| S/PDIF       | Sony/Philips Digital Interconnect Format, an optical or coaxial interface for audio signals                                                                        |  |  |  |  |

| SATA         | Serial ATA, high-speed differential signaling interface for hard drives and SSD                                                                                    |  |  |  |  |

| SD           | Secure Digital, flash memory card                                                                                                                                  |  |  |  |  |

| SDIO         | Secure Digital Input Output, an external bus for peripherals that uses the SD interface                                                                            |  |  |  |  |

| SIM          | Subscriber Identification Module, an identification card for GSM phones                                                                                            |  |  |  |  |

| SMBus        | System Management Bus (SMB), a two-wire bus based on the I <sup>2</sup> C specifications, is used primarily in x86 design for system management.                   |  |  |  |  |

| SoC          | System on a Chip, IC which integrates the main component of a computer on a single chip                                                                            |  |  |  |  |

| SPI          | Serial Peripheral Interface Bus, a synchronous four-wire full-duplex bus for peripherals                                                                           |  |  |  |  |

| TIM          | Thermal Interface Material, a thermally conductive material between CPU and heat spreader or heat sink                                                             |  |  |  |  |

| TMDS         | Transition-Minimized Differential Signaling, serial high-speed transmitting technology that is used by DVI and HDMI                                                |  |  |  |  |

| TVS Diode    | Transient-Voltage-Suppression Diode, a diode that is used to protect interfaces against voltage spikes                                                             |  |  |  |  |

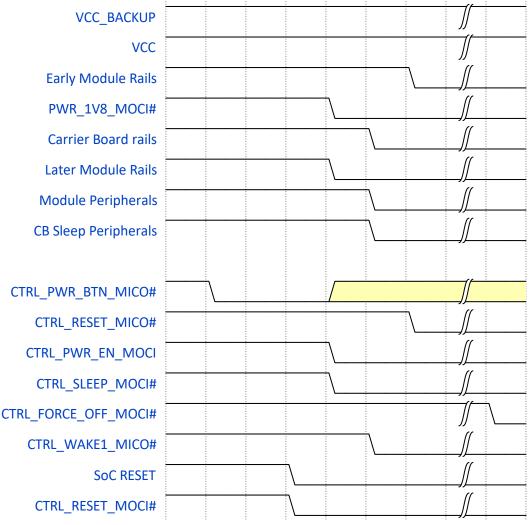

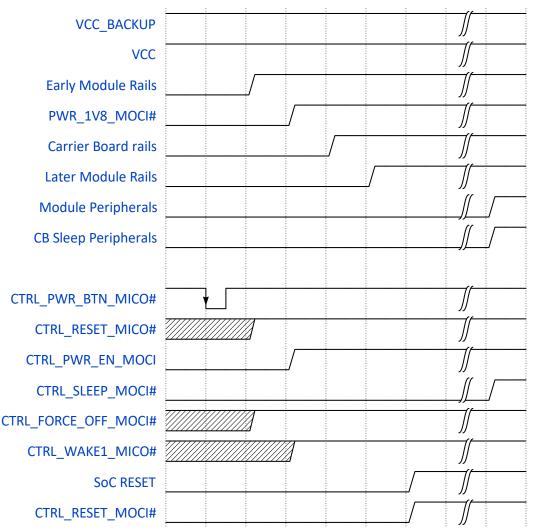

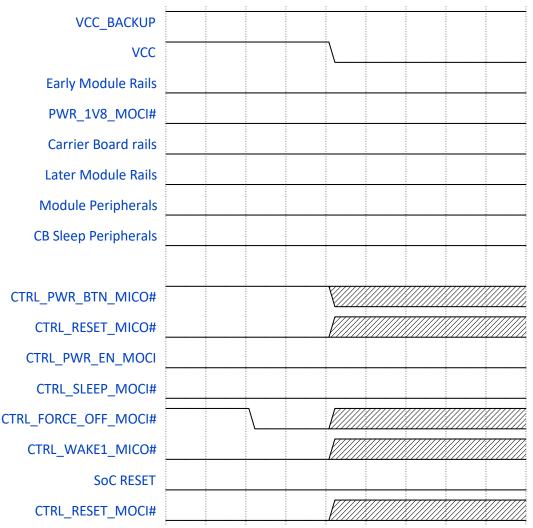

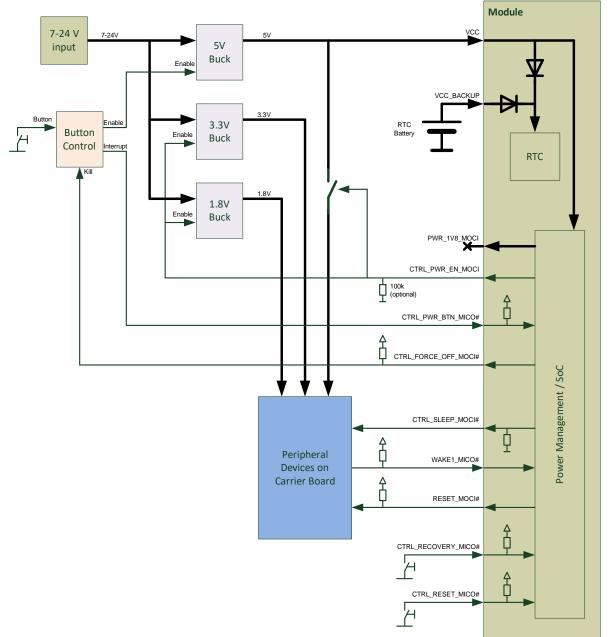

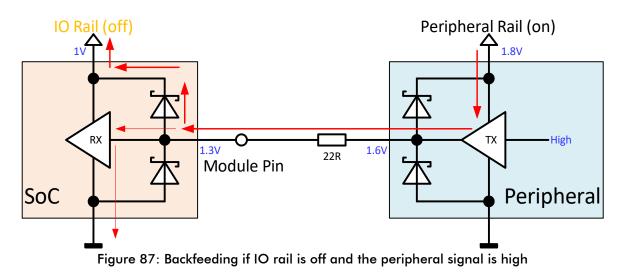

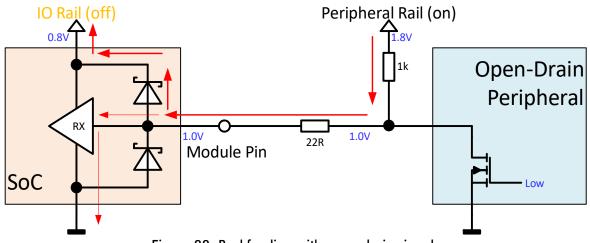

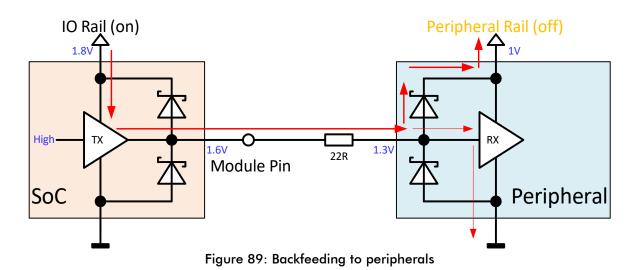

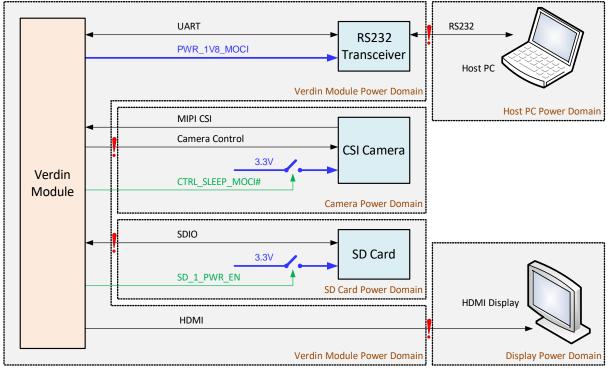

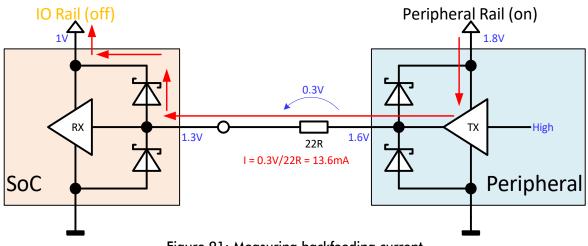

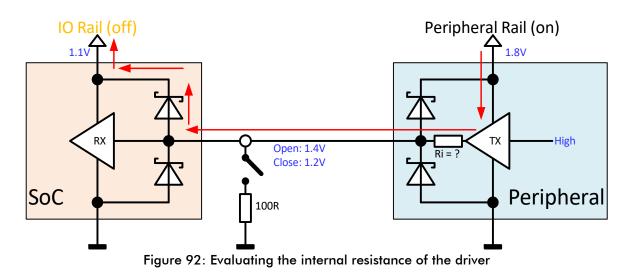

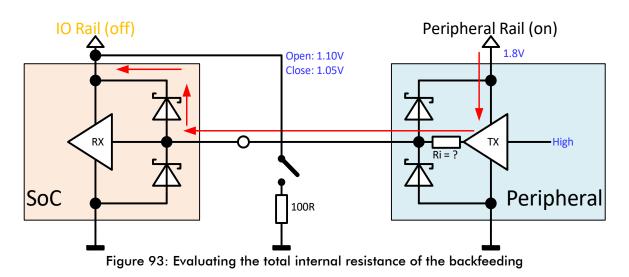

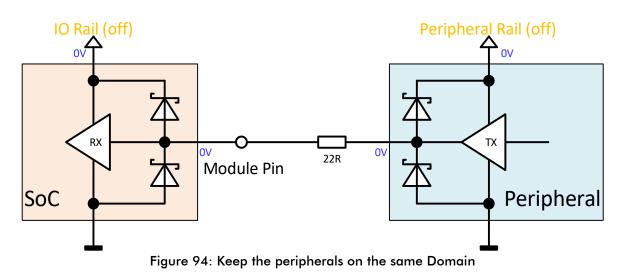

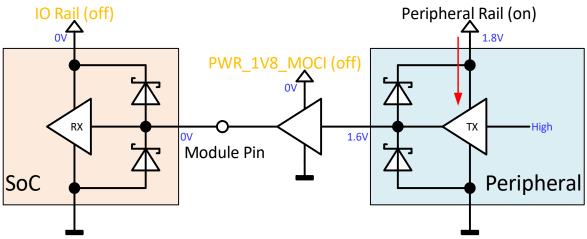

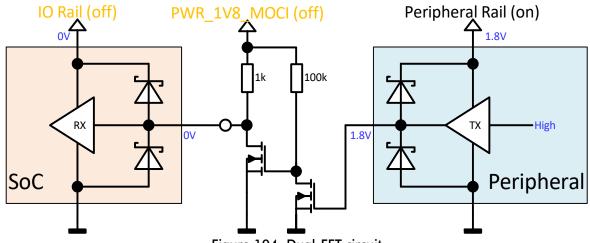

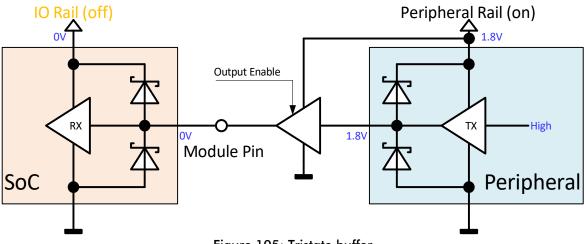

| UFP          | Upstream Facing Port, USB Type-C port that acts as a client                                                                                                        |  |  |  |  |